当我们在采购选择晶振频率元件时,首先要了解其详细的各项参数,如频率及负载电容是主要的,负载电容没有选择恰当,那么将无法与产品相匹配.如当订购工作频率为f(如32.768千赫或20兆赫)的振荡器晶体时,通常仅规定工作频率是不够的.虽然晶体将以接近其串联谐振频率的频率振荡,但实际振荡频率通常与该频率略有不同(在"并联谐振电路"中稍高些).

1.所以,假设你有一个晶体振荡器电路,你想购买晶体,当放置在这个电路中时,振荡频率是f.你需要告诉晶体制造商什么来完成这个?您是否需要发送振荡器设计示意图及其所有相关设计细节,例如电容,电阻,有源元件和布局相关杂散的选择?幸运的是,答案是否定的.除了频率f,所需要的只是一个数字,即负载电容C1.

2.什么是CL?

假设您的石英晶体振荡器工作在所需的频率f.在该频率下,晶体具有复阻抗Z,对于工作频率而言,这是晶体唯一重要的特性.因此,要使振荡器在频率f下工作,你需要在频率f下具有阻抗Z的晶体.所以,在最坏的情况下,你只需要指定一个复数Z=R+jX.事实上,它甚至比这更简单.

虽然原则上应该指定频率为f的晶体电阻,但通常晶体间电阻的变化以及振荡器对这种变化的灵敏度都足够低,因此不需要指定电阻.这并不是说晶体电阻没有作用;确实如此.我们将在第4节中进一步讨论这一点.

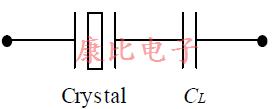

所以,剩下一个值来指定:f时的晶体电抗.所以,我们可以指定一个在20兆赫时电抗为400ω的晶体.然而,这通常是通过指定电容C1和等式来实现的其中我们已经设置ω=2πf.在物理上,在该频率下,石英晶振和电容C1的串联组合的阻抗具有零相位(等效地,具有零电抗或纯电阻).参见图1.要看到这一点,请考虑

其中第二步遵循等式(1)和电容C的电抗为-1/(ωC)的事实.

因此,确保适当振荡频率的任务是提供在指定频率下具有所需电抗的元件(在这种情况下为晶体),该电抗由等式(1)用电容C1来表示.2例如,我们不是指定在20MHz下电抗为400ω的晶体,而是指定在20MHz下负载电容为20pF的晶体,或者更正常地,我们指定在20pF的负载电容下晶体频率为20MHz晶振.

在"并联谐振电路"中,CL是正的,通常在5pF和40pF之间.在这种情况下,晶体工作在晶体串联和并联谐振频率(分别为Fs和Fp)之间的窄频带.

虽然真正的"串联谐振电路"没有与其相关联的负载电容[或者可能是等式(1)中的无限值,但是大多数“串联谐振电路”实际上稍微偏离串联谐振频率工作,因此确实具有有限的负载电容(可以是正的或者负的).但是,如果该偏移很小,并且不希望指定负载电容,则可以忽略该偏移,也可以在指定频率f内稍微偏移一点.

正如我们将在第4节中看到的,振荡器和压电石英晶体决定CL.然而,晶体的作用相当弱,因为在零电阻的极限下,晶体在确定CL方面根本不起作用.在这种限制情况下,称CL为振荡器负载电容是有意义的,因为它完全由振荡器决定.然而,当需要订购晶体时,可以指定负载电容C1处的频率为f的晶体,即这是晶体频率的一个条件.因此,将CL称为晶体负载电容是合理的.为了便于讨论,我们简单地避免了这个问题,并使用了负载电容一词.

3.在CL处定义FL

现在我们把等式(1)作为我们对在给定负载电容下具有给定频率的晶体的定义.

定义:当晶体在负载电容C1处的电抗X由等式(1)给出时,晶体在负载电容C1处具有频率F1,其中ω=2πF1.

回想一下,在给定的模式下,贴片晶振的电抗从负值,通过串联谐振时的零点,增加到并联谐振附近的大正值,在那里它迅速降低到大负值,然后再向零增加.(参见参考[1).)通过排除并联谐振周围的区域,每个电抗值都有一个单一的频率.以这种方式,我们可以给定C1值来关联频率F1.因此,CL的正值对应于串联和并联谐振器之间的频率.CL的大负值对应于串联谐振以下的频率,而较小负值对应于并联谐振以上的频率.(见下面的等式(3).)

3.1.晶体频率方程

那么,振荡频率在多大程度上取决于负载电容C1?我们可以通过确定晶体频率F1如何取决于晶体负载电容C1来回答这个问题.人们可以很好地证明

(图1)

其中C1和C0分别是晶体的运动电容和静态电容.(参见参考[1]了解这一关系的推导和讨论.)在本笔记中,我们将公式(3)称为晶体频率公式.这表明晶体振荡器的工作频率对其负载电容的依赖性以及对晶振本身的依赖性.具体而言,当负载电容从CL1变为CL2时,分数频率变化由给出如图1所示.